芯片特性

- Marvell 88E6321/88E6320 是一个7-Port千兆以太网交换芯片。支持最新的IEEEE802.1 Audio Video Bridging标准。

- 芯片包含两个10、100、1000三速以太网收发器(PHYs),两个千兆SERDES,三个数字接口(GMIIRGMIIMII组合)。

- 芯片采用Marvell动态队列限制(Dynamic Queue Limit ),实现高速无阻塞4级QOS交换结构。包含一个高性能地址查询引擎,多达支持8K个节点和1Mbit的帧缓存。

- 内部MAC单元符合标准的IEEE802.3,最大支持10KByte帧长。

- 包含一个TCAM-based策略控制列表(TCAM-based Policy Control List)引擎,支持256条规则(仅88E6321支持)。

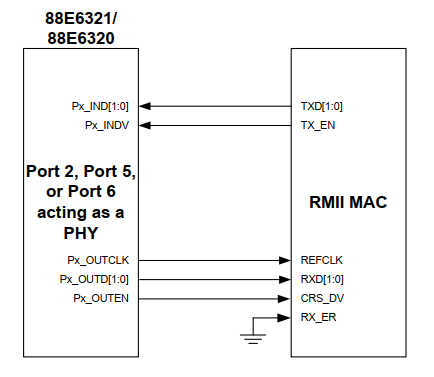

- 芯片的RGMII(或MII/RMII)接口支持直接连接管理器件或者路由器CPU作为MAC使用。2、6Port可以设置支持完整GMII接口。

- 千兆SERDES接口支持SGMII、1000BASE-X、100BASE-FX。

- PHY单元支持802.3az 节能以太网(Energy Efficient Ethernet)。

- 内部PHY单元、MAC单元均支持完整IEEE802.3标准。

- 支持帧唤醒和帧时间侦测唤醒功能,允许在连接cpu是进入睡眠模式,以达到降低系统功耗目的。

- 多达6个LED,可以通过寄存器配置相应功能。

- 可以使用SMI接口和以太网帧对芯片进行配置,也可以使用EEPROM进行配置。

- 支持8K条MAC地址自动学习和老化功能。

- 支持25MhzXTAL时钟源。

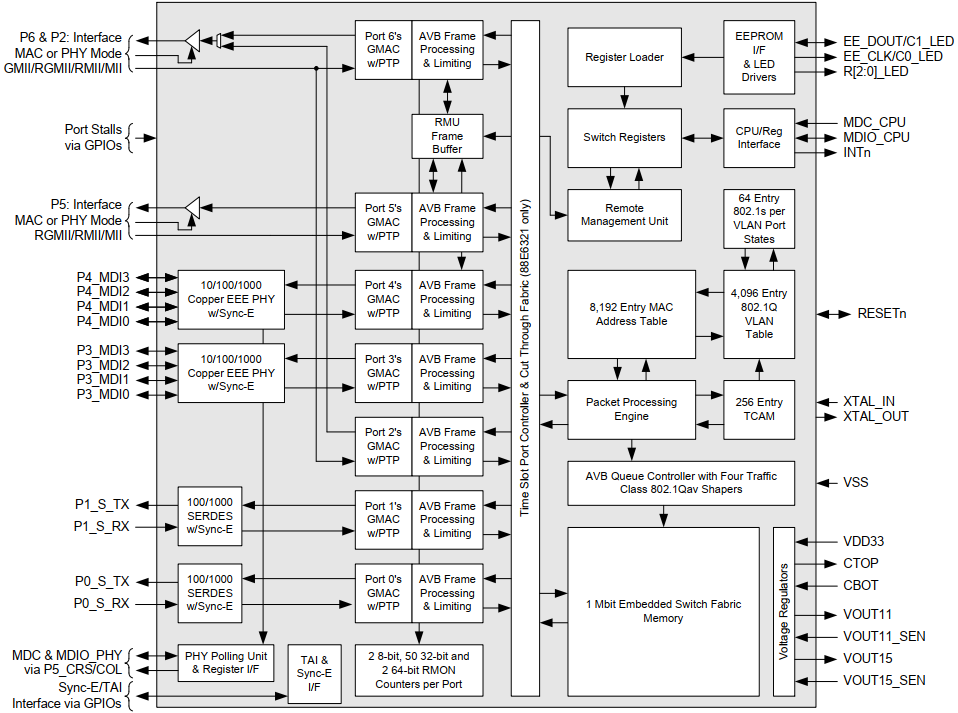

结构框图

从结构框图可以看出:

- Port2、5、6可以配置为MAC模式或者PHY模式,均支持RGMII/RMII/MII,2、6Port还支持GMII。

- Port3、4支持10、100、1000M自适应以太网接口。

- Port0、1支持100M、1000M光口(SFP)。

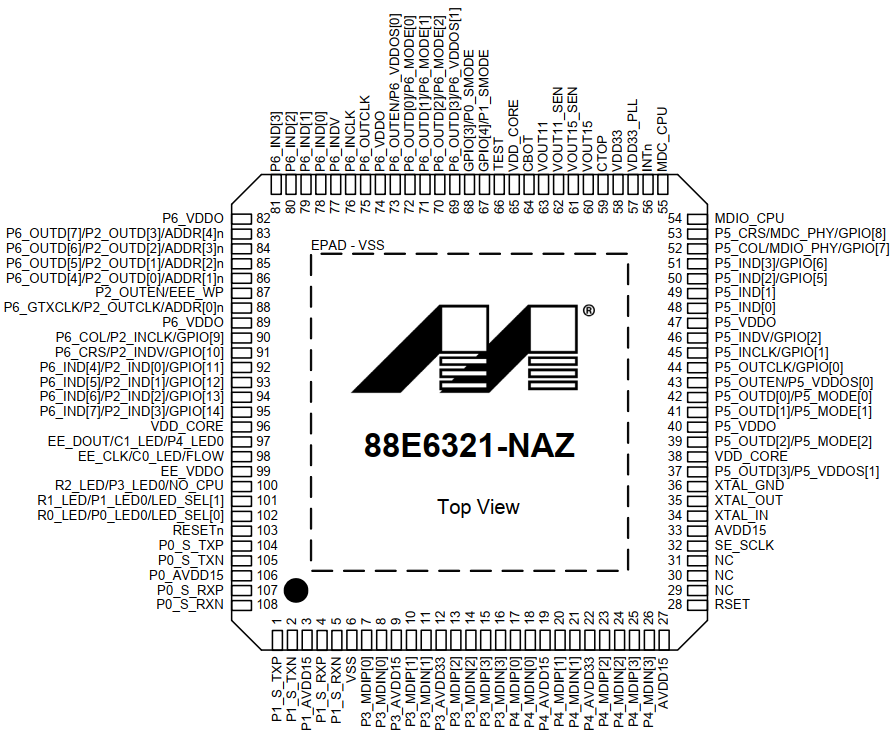

引脚定义

从引脚定义可以看出,许多引脚都有多种功能,这些复用的功能大多在RESETn为低电平时有效,RESETn上升沿时锁存。

1.NO_CPU模式选择:

在复位状态下(RESETn = low)时,设置NO_CPU引脚电平后,RESETn上升沿将锁存引脚电平。若此时NO_CPU=0则表示芯片由CPU控制,NO_CPU=1则表示芯片非CPU控制。

在NO_CPU=0模式下,所有的Port在初始化时都被关闭,PHY的供电关闭,使得CPU可以在芯片工作前进行启动与配置,该引脚内部上拉,默认上电所有Port打开。

为了方便,可以将NO_CPU置为1进行调试,调试通过后,考虑低功耗处理时,可以采用NO_CPU=0模式,以屏蔽不需要打开的Port。

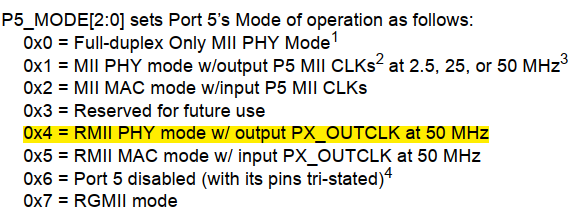

2.P5和P2、6的模式选择(以P5为例):

P5_OUT[3:0]为多功能引脚,在复位状态下(RESETn = low),引脚为输入状态,此时可以设置引脚电平(P5_MODE[2:0])来决定该端口的工作模式(见下图),在设置好引脚电平后,RESETn上升沿过程中将会锁存引脚电平,进入对应的工作模式。

该引脚内部上拉,默认工作模式为RGMII,对于其他模式,可以在硬件上直接串4.7K电阻到GND来进行配置,我这里设置为0x04RMII模式,因此P5_MODE[1:0]引脚通过4.7K电阻接地。

在NO_CPU=1模式下,P5_CRS,P5_COL作为MDC_PHY,MDIO_PHY功能使用用于管理外接的SMI从设备(如外部PHY),否则为GPIO[8:7]使用。

3.寻址模式

由于88E6321本身功能强大,即可以做MAC也可以做PHY(2个Port)、SERDES(2个Port),因此虽然只是一个芯片,但却可以看作多个设备,这将面临一个地址确定的问题,如何给片内PHY、SERDES、MAC分配地址。为了解决这个问题,88E6321有两种芯片寻址模式:单芯片寻址与多芯片寻址。

通过在复位状态时设置ADDR[4:0]n引脚的电平可以设置设备地址(需要注意的是,ADDR所设置的地址为实际SMI地址的反码,即ADDR=0x1F对应的实际SMI地址为0x00,,ADDR=0x00对应的实际SMI地址0x1F,这点在下文中需要注意)。

- 单芯片寻址模式:

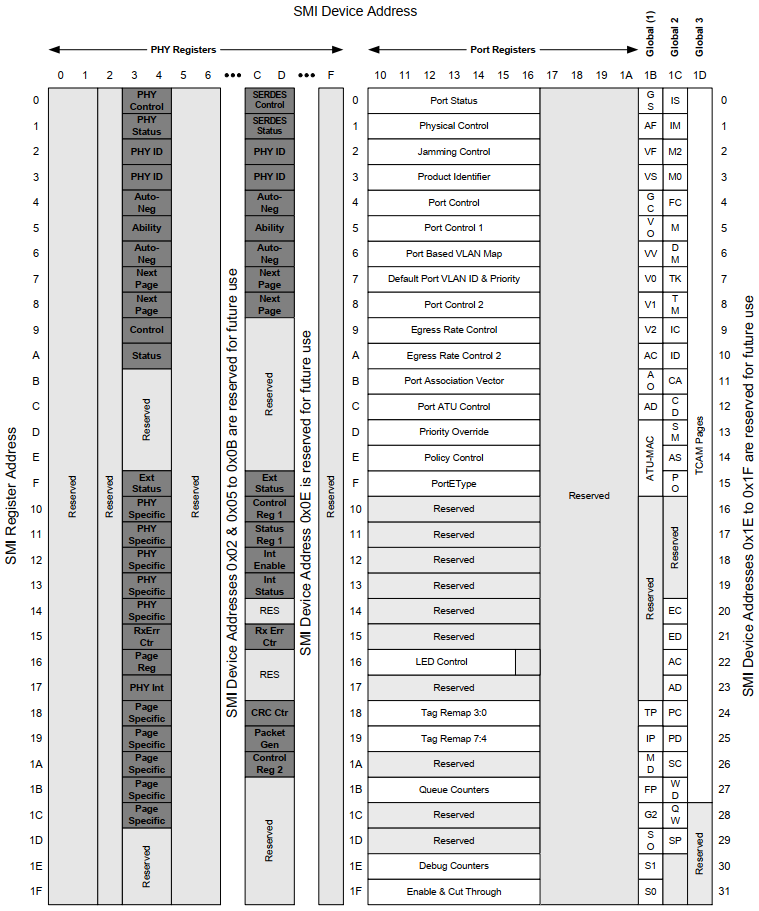

当ADDR[4:0]n=0x1F时,进入单芯片寻址模式,此时通过内部地址直接访问,在这个模式下,88E6321会响应所有的32个SMI地址,因此必须确保他是惟一的SMI从设备,在设备寄存器映射图中,SMI设备地址0X10-0X16(对应Port0-Port7),0X1B-0X1D(对应特殊寄存器Global1-3)是可以直接访问的,而地址0X03、0X04(对应Port3、4的PHY)、0X0C、0X0D(对应Port0、1的SERDES)则需要使用Global2地址的SMI PHY Command和SMI PHY Data两个寄存器进行间接访问。 - 多芯片寻址模式:

当ADDR[4:0]n!=0x1F时,则进入多芯片寻址模式,此时,88E6321只会响应ADDR设置的地址的反码,同时仅有两个寄存器可以直接访问(SMI Command寄存器与SMI Data寄存器),其他寄存器则通过这两个寄存器间接访问(包括在单芯片寻址模式下间接访问的寄存器)。

4.从SMI接口

当88E6321作为SMI从设备时,主控可以通过这个接口(MDC_CPU与MDIO_CPU)对88E6321进行管理。

MDC_CPU最高支持20MHz,MDIO_CPU需要外接一个4.7K到10K的上拉电阻。需要注意的是,该接口在INTn为低电平时才可以通信。

INTn为中断引脚,用于指示未被掩码屏蔽的中断是否产生。由于该引脚为开漏输出,且低电平有效,因此必须在其外部上拉,这样在未发生中断的情况下,始终未高电平。同时,该引脚低电平有效时也意味着SMI接口可以使用。(上电过程中,芯片会从外挂的EEPROM(如果有的话)加载寄存器设置,然后发出EEPROM处理完成中断,拉低INTn)

5.PHY接口

Port3、Port4支持10/100/1000三速PHY,支持IEEE标准中的10BASE-T,100BASE-TX,1000BASE-T。

6.SERDES接口

Port0、Port1是SERDES接口,可以通过配置选则其工作模式:

- 连接Marvell的三速PHY

SERDES可以配置为三速PHY接口,用于连接外部PHY,此时SERDES使用SGMII协议, - 连接到1000BASE-X的光纤模块

- SGMII接口

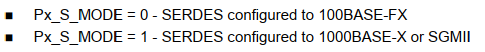

通过设置Px_SMODE引脚电平可以配置SERDES工作模式:

- 与其他Marvell交换芯片级联

LED接口

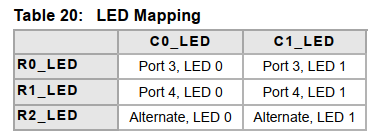

88E6321采用矩阵LED接口,使得每个PHYPort都能分配到2个LED。LED的阴极都连接到一条行信号线上(Rx_LED),阳极连接到列信号线上(Cx_LED)。LED引脚能够形成3行2列的矩阵LED。

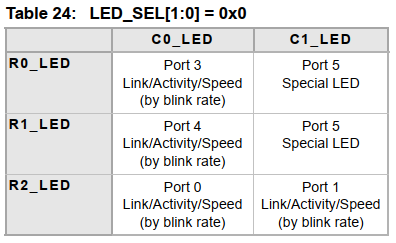

LED映射如下图:

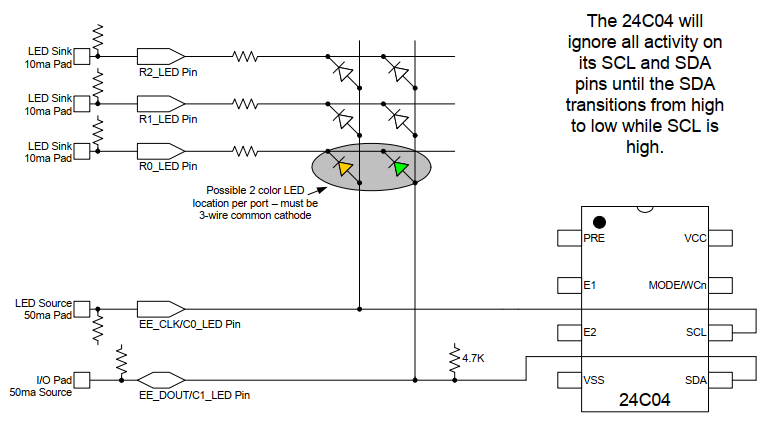

典型电路连接图:

LED行信号(Cx_LED)与EEPROM共用,采用时分多路复用来避免LED与EEPROM操作的互相干扰。

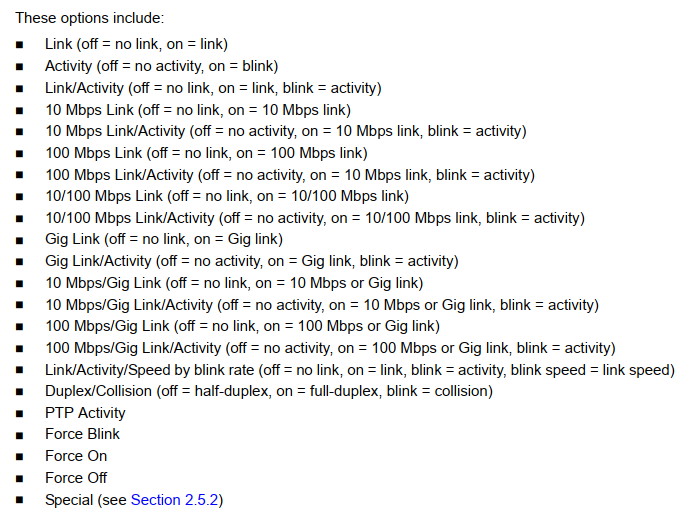

- LED选项

通过对各自Port的LED Control寄存器(offset=0x16)进行配置,可以设置各个LED的功能:

- 上电参数设置

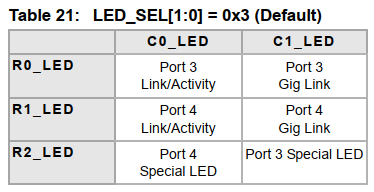

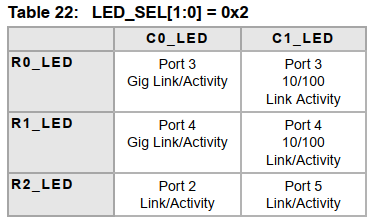

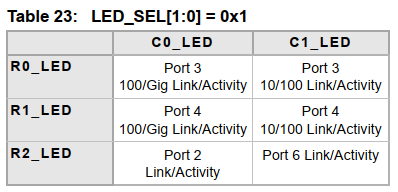

LED上电后的初始化功能可以由LED_SEL[1:0]来配置,这些硬件内部上拉,默认是0x03,可以复位状态通过外接下拉4.7K电阻,来改变初始配置。

1.LED_SEL[1:0]=0x03

一个LED显示网络连接(Link)与网络活动(Activity),另一个LED用于显示更高速率的连接(Gig Link)。

2.LED_SEL[1:0]=0x02

一个LED显示千兆网络连接与网络活动,另一个LED用于显示10/100M网络连接与网络活动.

3.LED_SEL[1:0]=0x01

用于双色或三色LED,不同颜色显示不同网络速率下的网络连接与网络活动。

4.LED_SEL[1:0]=0x00

用于单LED显示,通过不同的闪烁频率来表示不同网络速率,连接,网络活动。默认的闪烁频率如下:1Gbps:84ms,100Mbps:170ms,10M:340ms。

以上是88E6321关于硬件相关的介绍。

我这里使用stm32通过RMII连接至88E6321的Port5,Port4连接电口以太网,Port5连接SFP光口以太网。

不同于一般的功能单一的PHY器件(如LNA8720A),88E6321的PHY相关寄存器操作相对较复杂,具体操作方法见后续介绍。

您好,我们也想用88E6321设计一款板子,能分享下设计方案么,报酬详谈,QQ705484965